# SIMULATION OF 5 LEVEL THREE PHASE CASCADE H-BRIDGE MULTI LEVEL INVERTER

## T. Manmadha Rao

Assistant Professor,

Department of EEE,

Aditya Institute of Technology and

Management

## B. Raja Sekhar

UG Scholar ,

Department of EEE,

Aditya Institute of Technology and

Management

## K. Hari Krishna

UG Scholar , Department of EEE, Aditya Institute of Technology and Management

### G. Pavan Kumar

UG Scholar,

Department of EEE,

Aditya Institute of Technology and

Management

#### M. Hari Krishna

UG Scholar,

Department of EEE,

Aditya Institute of Technology and Management

## 1. ABSTRACT

The traditional inverters have the drawbacks of Harmonics as well as Total Harmonic Distortion (THD). In Multilevel inverters (MLI), Cascaded H-bridge(CHB) Multilevel inverter is most efficient topology for medium and high voltage applications that reduces the Total Harmonic Distortion. The mode of operation for suggested inverter topology has been described. The design of the proposed 3-phase 5-level CHB inverter and simulation outcomes are performed by the MATLAB/Simulink.

**KEY WORDS:** Total Harmonic Distortion (THD), Multilevel inverters (MLI), Cascaded H-bridge(CHB), Pulse width modulation(PWM), etc.

### 2. INTRODUCTION

A device that converts DC power into AC power at desired output voltage and frequency is called an Inverter. Phase controlled converters when operated in the inverter mode are called line commutated inverters. But line commutated inverters require at the output terminals an existing AC supply which is used for their commutation. This means that line commutated inverters can't function as isolated AC voltage sources or as variable frequency generators with DC power at the input. Therefore, voltage level, frequency and waveform on the AC side of the line commutated inverters can't be changed. On the other hand, force commutated inverters provide an independent AC output voltage of adjustable voltage and adjustable frequency and have therefore much wider application.

Inverters can be broadly classified into two types based on their operation:

- Voltage Source Inverters(VSI)

- Current Source Inverters(CSI)

Multilevel inverters continue to receive more and more attention because of their high voltage operation capability, low switching losses, high efficiency and low output of Electro Magnetic Interference (EMI). The term multilevel starts with the three-level inverter introduced by Nabae et ala(1981). Now a days, multilevel inverters are becoming increasingly popular in power applications, as multilevel inverters have the ability to meet the increasing demand of power rating and power quality associated with reduced harmonic distortion and lower electromagnetic interference. A multilevel inverter has several advantages over a conventional

# EPRA International Journal of Multidisciplinary Research (IJMR) - Peer Reviewed Journal

Volume: 6 | Issue: 12 | December 2020 | | Journal DOI: 10.36713/epra2013 | | SJIF Impact Factor: 7.032 | | ISI Value: 1.188

two-level inverter that uses high switching frequency pulse width

Modulation (PWM). The most attractive features of a multilevel inverter are as follow

- 1. They can generate output voltages with extremely low distortion and lower dv/dt.

- 2. They draw input current with very low distortion. 3) They generate smaller common mode (CM) voltage.

- 3. They can operate with a lower switching frequency.

Multilevel Power Inverter (MPI) represent a valid alternative in spite of converter". The use of MPIs is now very widespread in that applications with medium voltage and high power because for medium and high voltage power applications, power semiconductor switches present operative limits. Moreover, these types of converters are widely used to interface with the electrical grids the renewable energy systems like PV systems, wind farms, Fuel Cell based systems and are also used in electrical drive systems. One of the main advantages of this kind of converters is the low harmonic content in output voltage waveforms. In literature, the harmonic content reduction in output voltage and current waveforms of the converters have been largely discussed in the last years. Many modulation techniques, i.e. the pulse width modulation based ones, uses triangular waveform as carrier signals. In some studies, have been developed new modulation techniques in which the carrier signals are changed. In particular, the use of carrier signals with different harmonic content, respect triangle waveform, allows to change the harmonic content in the output voltage waveform of the converter.

The operation of CHB MLI and gating signals generation are explained in chapter-3(Methodology), Designed Simulation circuit for 3-phase CHB MLI and the results are explained in chapter-4 (Simulation Circuits And It's Results). Lastly conclusion and references given in chapter-5 and chapter-6 respectively.

#### 3. METHODOLOGY

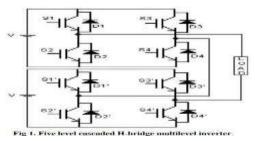

## • CASCADED H-BRIDGE MULTI LEVEL INVERTER

In a five level cascaded H-bridge multilevel inverter The inverter consist of two H-bridge with series connection and each H-bridge having separate dc source. Which is fed by self-sufficient dc voltage source. In this figure two H-bridge consist of 8-MOSFET switches each H-bridge having 4MOSFET switches. This two H-bridge switches are worked as two H-bridge series connection. So, first H- bridge switches are S1, S4 and second H-bridge switches are S1', S4' open at time S2, S3 same as second bridge S2', S3' are off. So output will be wave form of staircase. If number of level increase the number of dc source increases. It will be effect on cost of dc

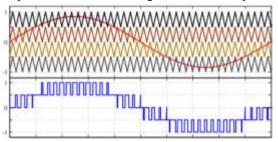

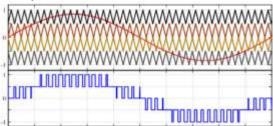

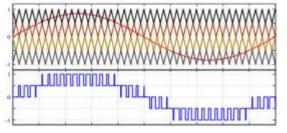

source and switches with complexity of inverter design circuit. This is disadvantages. The multilevel inverter are used where the demand of high power and power quality are essential, for example UPS, photo voltaic power conversion and hybrid power trains. Fig3 show the methodology of 5-level inverter analysis in matlab. First we have taken modulation index that is indicates of the ratio of peak magnitude of the modulation waveform and carrier waveform. It is relates the inverter dc-link voltage output of inverter. The modulation signal and magnitude of triangular signal vary between the peak magnitude and lower magnitude. The ratio of peak magnitude of modulation wave and the carrier wave is define as modulation index. Then comes to comparison of sine and triangular wave. In this comparison sine wave is fixed and four triangular wave vary by the modulation index. It will be given wave form of pulses. Then comes to PWM (pulse with modulation) generation. That is indicates comparison of sine and triangular wave form and it gave wave form of pulses that is given to switches. After then comes to FFT analysis.

# • SINUSOIDAL PULSE WIDTH MODULATION

In sinusoidal PWM instead of maintaining the width of all pulses the same as in the case of multiple PWM, the width of each is varied in proportion to the amplitude of a sine wave evaluated at the same pulse. The distortion is reduced significantly compared to multiple PWM. A high frequency triangular wave, called the carrier wave, is compared to a sinusoidal signal representing the desired output, called the reference wave. Usually, ordinary signal generators produce these signals. Whenever the carrier wave is less than the reference, a comparator produces a high output signal, which turns the upper transistor in one leg of the inverter on the lower switch off. In the other case the comparator sets the firing signal low, which turns the lower switch ON and upper switch OFF. The number of pulses per half cycle depends on the carrier frequency. Within the constraint that two transistors of the same arm cannot conduct at same time, the instantaneous output voltage is shown in Figure the same gating signals can be generated by using unidirectional triangular carrier wave as in Figure this method is preferable and easier to implement. The output voltage can be varied by

# $EPRA\ International\ Journal\ of\ Multidisciplinary\ Research\ (IJMR)\ -\ Peer\ Reviewed\ Journal$

Volume: 6 | Issue: 12 | December 2020 | | Journal DOI: 10.36713/epra2013 | | SJIF Impact Factor: 7.032 | ISI Value: 1.188

varying the modulation index 'm'. The area of each pulse corresponds approximately to the area under the sine wave between the adjacent mid points of off-periods on the gating signals

The The SPWM, which is most commonly used, suffers from certain drawbacks like low fundamental output voltage.

#### **MULTI CARRIER PWM**

Multiple Pulse Width Modulation Technique is used in three level or more than three levels. These are classified into two types: - Level Shift, Phase Shift. Level Shifted PWM (LS-PWM)

N-1 carrier signals are used which are vertically shifted to each other. A level-shifted PWM can be classified in three types:

- 1. Phase Disposition (PD-PWM)

- 2. Phase Opposition Disposition (POD-PWM)

- 3. Alternative Phase opposition Disposition (APOD-PWM)

1.Phase Disposition (PD-PWM): In Phase Disposition all the carrier signals are in same phase.

2.Phase Opposition Disposition (POD-PWM): In Phase Opposition Disposition all the carrier signals above the zero are out of phase with those below the zero by 180°.

3.Alternative Phase opposition Disposition (APOD-PWM): In Alternate Phase Opposition Disposition all the adjacent carrier signals are out of phase by 180°.

In this paper, Phase disposition PWM technique is used to get the gating signals for MOSFETS.

# 4. SIMULATION CIRCUITS AND IT'S RESULTS

The multilevel cascade inverter synthesizes its output nearly sinusoidal voltage waveforms by combining many isolated voltage levels. A series of single-phase full bridges makes up a phase for the inverter. A single-phase multilevel cascade Inverter topology is essentially composed of single identical phase legs of the series-chain of H-bridge inverter, which can possibly generate different output voltage waveforms and offers the potential for ac system phase-balancing. This feature is impossible in other Voltage source control topologies utilizing a common dc link. Since this topology consists of series power conversion cells, the voltage and power level may be easily amplified. The dc link supply for each full bridge inverter is provided separately, and this is typically achieved using diode rectifiers without using the single-phase transformer. The converter topology is based on the series connection of singlephase inverters with separate dc sources the resulting phase voltage is synthesized by the addition of the voltages generated by the different cells. For example in a five level cascaded inverter each single-phase full-bridge inverter generates five voltages at the output:+Vdc, + 2vdc, 0,-Vdc and -2Vdc. As Multilevel inverter is made up of semiconductor switches which are very sensitive to disturbances and become less tolerant to power quality problems such as under voltage and over voltage. So a suitable controller is required to maintain constant voltage. The existing model shows the H-bridge configuration of a 5 level multilevel inverter. Based on the triggering gate pulses the switches conduct. Thus output is obtained in form of levels. [12] In our paper we are presenting a H-bridge inverter model working on three phase AC supply. For real time implementation we are using MOSFET/IGBT as the switches. The control strategy is simple pulse width modulation technique (PWM) is used to control the gate pulses. Our model uses 7 H-Bridges of four power switches for synthesising a phase voltage. Each switch conducts for a particular time period based on the firing angle given to them. At any point of time only one switch is in conduction from one leg. No two switches from the same leg are in conduction at the same time. A pulse generator is implemented to provide width modulation and controlling the gate pulses. The initial source for the inverter is existing AC supply. Using a three phase rectifier the AC voltage is converted to DC voltage. Suitable filters are used to get a undistorted wave form. This is fed to each inverter leg. Separate DC sources are added to each leg. The output voltage is the cumulative sum of phase voltage across each leg. In this way different legs are cascaded to synthesise the levels. Thus the

# EPRA International Journal of Multidisciplinary Research (IJMR) - Peer Reviewed Journal

Volume: 6 | Issue: 12 | December 2020 | | Journal DOI: 10.36713/epra2013 | | SJIF Impact Factor: 7.032 | | ISI Value: 1.188

H-bridge topology produces voltage levels obtained as a summation of individual voltages.

A capacitor may be added sometimes to split the DC source Voltage into two halves. The voltage across each capacitor is VDC/2. In the proposed model 15 levels are synthesised using 7 sublevels of H-bridge with 28 switches for each phase of the three phase output. This comprises the circuit for DC to AC conversion using cascaded H-bridge inverter. Suitable filters are designed and added to the output so that a near sinusoidal three phase waveform is obtained The gate pulses are controlled using simple PWM technique. A pwm pulse generator is used to provide gate pulses for the gates of the switches. In this technique the width of the pulses are varied to vary firing angles of the thyristors. In pwm method the carrier wave and reference wave superimposed on each other and compared. This logic serves as the difference in conduction of switches resulting in a pulsating AC output. There are many forms of modulation used for communicating information. When a high frequency signal has amplitude varied in response to a lower frequency signal we have AM (amplitude modulation). When the signal frequency is varied in response to the modulating signal we have FM (frequency modulation). These signals are used for radio modulation because the high frequency carrier signal is needs for efficient radiation of the signal. When communication by pulses was introduced, the amplitude, frequency and pulse width become possible modulation options. In many power electronic converters where the output voltage can be one of two values the only option is modulation of average conduction time.

The basic principle used for the pwm technique is: PWM signal = sgn (r(t)-g(t))Where r(t) - reference signal g(t)-carrier signal.

Fig:Simulation circuit of 3-phase 5-Level CHB

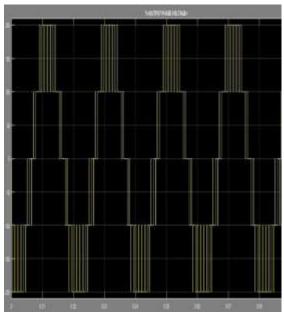

Fig: Control circuit for 3-phase 5-Level CHB MLI

# EPRA International Journal of Multidisciplinary Research (IJMR) - Peer Reviewed Journal

Volume: 6 | Issue: 12 | December 2020 | | Journal DOI: 10.36713/epra2013 | | SJIF Impact Factor: 7.032 | | ISI Value: 1.188

In three phase 5-level CHB MLI, the THD is 5.63%, which is shown in FFT window.

Fig: THD analysis of 3-phase 5-Level CHB MLI

In the Output Phase voltage wave form of 3-phase 5-Level CHB MLI, we got 5 levels i.e. 0V, +100V, +200, - 100V, and -200V.

Fig: Output Phase voltage wave form of 3phase 5-Level CHB MLI

### 5. CONCLUSION

In this paper, Designed a circuit for three phase 5 level Cascaded H-Bridge Multi Level Inverter, the gate signals were generated by Sinusoidal Multi carrier Pulse width modulation technique (Phase disposition PWM) and simulated in matlab/simulink. In the output phase voltage waveform, we got five levels and analyzed the THD analysis.

### 6. REFERENCES

- 1. A. Jain, N. Khatri, P. Shrivastav and A. Mahor "THD Analysis of Cascaded H-bridge Multilevel Applications" Inverters in FuelCellIEEEInternational Conference on Computer, Communication and Control, 2015, pp 1-6

- 2. B. Rajesh and Manjesh "Comparison of Harmonics and THD Suppression with Three and 5 Level Multilevel Inverter-Cascaded H-bridge" IEEEInternational Conference on Circuit, Power and Computing Technologies[ICCPCT], 2016, pp 1-6

- A. K. Ranjan, D. V. Bhaskar and N. Parida "Analysis and Simulation of Cascaded H-bridge Multi Level Inverter Using Level-Shift PWM Technique " IEEE International Conference on Circuit, Power and Computing Technologies [ICCPCT], 2015, pp 1-5

- 4. E. T. Renani, M. Fathi, M. Elias and N. A. Rahim "Performance evaluation of multicarrier PWM methods for cascaded H-bridge multilevel inverter " IEEE 3rd IET International Conference on Clean Energy and Technology (CEAT), 2014, pp 1-5.