SJIF Impact Factor: 6.260| ISI I.F.Value:1.241| Journal DOI: 10.36713/epra2016 ISSN: 2455-7838(Online)

### EPRA International Journal of Research and Development (IJRD)

Volume: 5 | Issue: 2 | February 2020 - Peer Reviewed Journal

# DESIGN OF LOW-POWER FULL SWING MIXED-LOGIC LINE DECODERS IN 32nm SCALING TECHNOLOGY

# Matcha Pavani<sup>1</sup>,

Raghu Institute of Technology

# Dr. P.S.R Chowdary<sup>2</sup>

Raghu Institute of Technology

### **ABSTRACT**

The invention of integrated circuits there has been a continuous demand for high performance, low power and low area or low cost diversified application from a variety of consumers. This demand has been pushing the fabrication process sub micron technologies such as 32, 22, 14nm and so on. The various technology aspects for low power applications are reviewed in detail, along with the evaluation of new technology, bearing in mind the power, performance and area. We are going to design 2-4 and 4-16 decoders with mixed logic design. Mixed logic is a gate-level design. It allows a digital logic circuit designer to separate the functional description of the circuit from its physical implementation. The use of mixed logic design provides logic expressions and logic diagrams that are analog of each other. In order to design these decoders there are two topologies are presented for the 2-4 decoder: a 14-transistor topology aiming on minimizing transistor count and power dissipation and 15-transistor topology aiming on high power-delay performance. Both normal and inverting decoders are implemented in each case, yielding a total of four new designs. Furthermore, four new 4-16 decoders will be designed by using mixed-logic 2-4 pre-decoders combined with standard CMOS post-decoder. All proposed decoders have full-swinging capability and reduced transistor count compared to their conventional CMOS counterparts. Finally, a variety of comparative Spice simulations at some area by using these comparative simulations we can show that the proposed circuits present a significant improvement in power and delay, outperforming CMOS in almost all cases.

INDEX TERMS—Line decoder, mixed-logic, power-delay optimization.

### I. INTRODUCTION

Very large scale integration (VLSI) is the process of creating an integrated circuit (IC) by combining thousands of transistors into a single chip. Over the past decade, power consumption of VLSI chips has constantly been increasing. Moore's Law drives VLSI technology to continuous increases in transistor densities and higher clock frequencies. The trends in VLSI technology scaling in the last few years show that the number of on-chip transistors increase about 40% every year. The operating frequency of VLSI systems increases about 30% every year. Although capacitances and supply voltages scale down meanwhile, power consumption of the VLSI chips is increasing continuously. On the other hand, cooling systems cannot improve as fast as the power consumption increases. Therefore in the very close future chips are expected to have

limitations of cooling system and solving this problem will be expensive and inefficient.

The main objective of Analysis of low power high performance 2-4 and 4-16 mixed line logic decoders is to reduce the power consumption. The power consumption can be reduced by minimizing the transistor count by using mixed logic design when compared to CMOS logic design. We design 2-4 and 4-16 decoders using mixed logic as well as CMOS logic and compare the results between them. In VLSI systems there is a trade-off between three parameters those are power, area and speed. To obtain better results in two parameters the third parameter should be negligible. Here we are designing low power and high performance decoders individually. So in order to design a low power and area efficient decoder speed has less preference. In order to design high performance and area efficient decoder power has less

### EPRA International Journal of Research and Development (IJRD)

- Peer Reviewed Journal Volume: 5 | Issue: 2 | February 2020

preference.

Line decoders are fundamental circuits, widely used in the peripheral circuitry of memory arrays.

#### **OVERVIEW OF LINE** II. **DECODER CIRCUITS**

In digital systems, discrete quantities of information are represented by binary codes. An *n*-bit binary code can represent up to  $2^n$  distinct elements of coded data. A decoder is a combinational circuit that converts binary information from *n* input lines to a maximum of  $2^n$  unique output lines or fewer if the *n*-bit coded information has unused combinations. The circuits examined here are n-to-m line decoders, which generate the  $m = 2^n \min$  terms of *n* input variables.

#### A. 2-4 Line Decoder

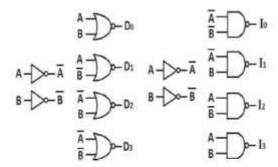

A 2-4 line decoder generates the 4 min terms D0-D3 of 2 input variables A and B. Its logic operation is summarized in Table I. Depending on the input combination; one of the 4 outputs is selected and set to 1, while the others are set to 0. An inverting 2–4 decoder generates the complementary min terms I0-I3, thus the selected output is set to 0 and the rest are set to 1, as shown in Table II. In conventional CMOS design, NAND and NOR gates are preferred to AND and OR, since they can be implemented with 4 transistors, as opposed to 6, therefore implementing logic functions with higher efficiency. A 2-4 decoder can be implemented with 2 inverters and 4 NOR gates Fig. 1(a), whereas an inverting decoder requires 2 inverters and 4 NAND gates Fig. 1(b), both yielding 20 transistors

Figure 1: a) Non Inverting NOR based Decoder. b) Inverter NAND based decoder

Table 1: Truth Table of 2-4 decoder

ISSN: 2455-7838(Online)

| A | В | D0 | D1 | D2 | D3 |

|---|---|----|----|----|----|

| 0 | 0 | 1  | 0  | 0  | 0  |

| 0 | 1 | 0  | 1  | 0  | 0  |

| 1 | 0 | 0  | 0  | 1  | 0  |

| 1 | 1 | 0  | 0  | 0  | 1  |

Table 2: Truth Table of Inverting 2-4 decoder

| Α | В | 10 | l1 | 12 | 13 |

|---|---|----|----|----|----|

| 0 | 0 | 0  | 1  | 1  | 1  |

| 0 | 1 | 1  | 0  | 1  | 1  |

| 1 | 0 | 1  | 1  | 0  | 1  |

| 1 | 1 | 1  | 1  | 1  | 0  |

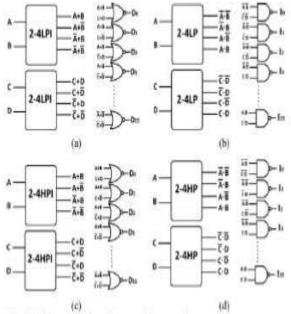

### B. 4-16 Line Decoder With 2-4 Pre decoders

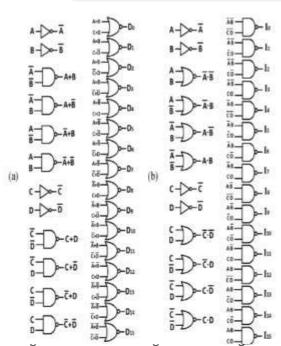

A 4-16 line decoder generates the 16 min terms  $D_{0-15}$  of 4 input variables A, B, C, and D, and an inverting 4-16 line decoder generates the complementary min terms  $I_0$  15. Such circuits can be implemented using a pre-decoding technique, according to which blocks of n address bits can be pre-decoded into 1-of-2<sup>n</sup> pre-decoded lines that serve as inputs to the final stage decoder [1]. Therefore, a 4–16 decoder can be implemented with 2 2-4 inverting decoders and 16 2-input NOR gates [Fig. 2(a)], and an inverting one can be implemented with 2 2-4 decoders and 16 2-input NAND gates [Fig. 2(b)]. In CMOS logic, these designs require 8 inverters and 24 2-input gates, yielding a total of 104 transistors each.

### EPRA International Journal of Research and Development (IJRD)

- Peer Reviewed Journal Volume: 5 | Issue: 2 | February 2020

decoders using 2-4 pre decoders and post decoders

#### III. **NEW MIXED-LOGIC DESIGNS**

Transmission gate logic (TGL) can efficiently implement AND/OR gates [5], thus it can be applied in line decoders. The 2-input TGL AND/OR gates are shown in Fig. 3(a) and (b), respectively. They are full-swinging, but not restoring for all input combinations. Regarding PTL, there are two main circuit styles: those that use nMOS-only pass transistor circuits, like CPL [3], and those that use both nMOS and pMOS pass transistors, like DPL [4] and DVL [6]. The style we consider in this work is DVL, which preserves the full swing operation of DPL with reduced transistor count [10]. The 2-input DVL AND/OR gates are shown in Fig. 3(c) and (d), respectively. They are full- swinging but nonrestoring, as well. Assuming that complementary inputs are available, the TGL/DVL gates require only 3 transistors. Decoders are high fan-out circuits, where few inverters can be used by multiple gates, thus using TGL and DVL can result to reduced transistor count. An important common characteristic of these gates is their asymmetric nature, ie the fact that they do not have balanced input loads. As shown in Fig. 3, we labeled the 2 gate inputs X and Y. In TGL gates, input X controls the gate terminals of all 3 transistors, while input Y propagates to the output node through the transmission gate. In DVL gates, input X controls 2 transistor gate terminals, while

input Y controls 1 gate terminal and propagates through a pass transistor to the output. We will refer to  $\hat{X}$  and Y as the control signal and propagate signal of the gate, respectively. Using a complementary input as the propagate signal is not a good practice, since the inverter added to the propagation path increases delay significantly. Therefore, when implementing the inhibition  $(A^{j}B)$  or implication  $(A^{j} + B)$  function, it is more efficient to choose the inverted variable as control signal. When implementing the AND (AB) or OR (A + B) function, either choice is equally efficient. Finally, when implementing the NAND  $(A^{j} + B^{j})$  or NOR  $(A^{j}B^{j})$  function, either choice results to a complementary propagate signal, perforce.

ISSN: 2455-7838(Online)

#### A. 14-Transistor 2-4 Low-Power **Topoloay**

Designing a 2-4 line decoder with either TGL or DVL gates would require a total of 16 transistors (12 for AND/OR gates and 4 for inverters). However, by mixing both AND gate types into the same topology and using proper signal arrangement, it is possible to eliminate

one of the two inverters, therefore reducing the total transistor count to 14.

Let us assume that, out of the two inputs, namely, A and B, we aim to eliminate the Binverter from the circuit. The  $D_o$  minterm  $(A^{j}B^{j})$  is implemented with a DVL gate, where A is used as the propagate signal. The  $D_1$  minterm (AB) is implemented with a TGL gate, where B is used as the propagate signal. The  $D_2$  minterm  $(A^{j}B)$  is implemented with a DVL gate, where A is used as the propagate Finally, The  $D_3$  minterm (AB) is implemented with a TGL gate, where B is used as the propagate signal. These particular choices completely avert the use of the complementary B signal; therefore, the Binverter can be eliminated from the circuit, resulting in a 14-transistor topology (9 nMOS and 5 pMOS). Following a similar procedure with OR gates, a 2-4 inverting line decoder can be implemented with 14 transistors (5 nMOS and 9 pMOS) as well:  $I_0$  and  $I_2$  are implemented with TGL (us- ing B as the propagate signal), and  $I_1$  and  $I_3$  are implemented with DVL (using A as the propagate signal). The B inverter can once again be elided. Inverter elimination reduces the transistor count, logical effort and overall switching activity of the circuits, thereby reducing power dissipation. The two new topologies are named "2-4LP" and "2-4LPI," where "LP" stands for "low power" and

### ISSN: 2455-7838(Online)

### EPRA International Journal of Research and Development (IJRD)

- Peer Reviewed Journal Volume: 5 | Issue: 2 | February 2020

"I" for "inverting." Their schematics are shown in Fig. 4(a) and (b), respectively.

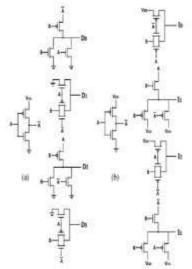

Figure 3: 2-4 decoder LP and LPI schematics B. 15-Transistor 2-4 High-Performance **Topology**

The low-power topologies presented above have a drawback regarding worst case delay. which comes from the use of complementary A

as the propagate signal in the case of  $D_0$  and  $I_3$ . However,  $D_0$  and  $I_3$  can be efficiently implemented using static CMOS gates, without using complementary sig- nals. Specifically,  $D_0$ can be implemented with a CMOS NOR gate and I<sub>3</sub> with a CMOS NAND gate, adding one transistor to each topology. The new 15T designs present a significant improvement in delay while only slightly increasing power dissipation. They are named "2–4HP" (9 nMOS, 6 pMOS) and "2–4HPI" (6 nMOS, 9 pMOS), where "HP" stands for "high performance" and "I" stands for "inverting." The 2-4HP and 2-4HPI schematics are shown in Fig. 5(a) and (b), respectively.

Figure 4: 2-4 decoder High Performance **Schematic and HPI schematic**

### Integration in 4-16 Line Decoders

PTL can realize logic functions with fewer transistors and smaller logical effort than CMOS. However, cascading PTL circuits may cause degradation in performance due to the lack of driving capability. Therefore, a mixed-topology approach, i.e., alternating PTL and CMOS logic, can potentially deliver optimum results.

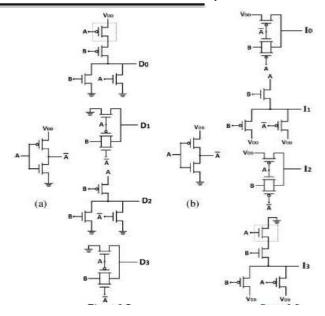

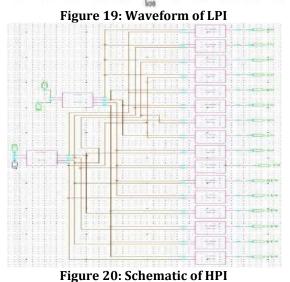

Figure 5: 4-16 Decoder LP, LPI, HP and HPI **Schematic**

#### SIMULATION RESULTS IV.

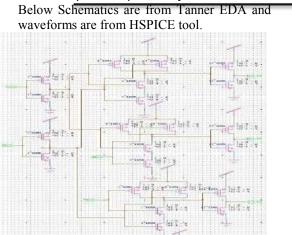

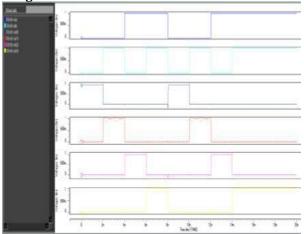

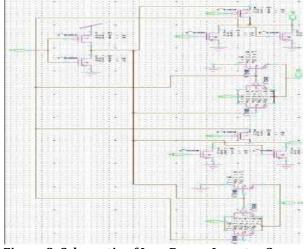

All the implementations are done in Tanner EDA tools and for power calculation we used HSPICE monte Carlo simulation methodology.

ISSN: 2455-7838(Online)

# **EPRA International Journal of Research and Development (IJRD)**

- Peer Reviewed Journal Volume: 5 | Issue: 2 | February 2020

Figure 6: Schematic of CMOS 2-4 decoder

Figure 7: Waveform of CMOS 2-4 Decoder

Figure 8: Schematic of Low Power Inverter 2-4 Decoder

Figure 9: Waveform of Low Power Inverter 2-4 Decoder

Figure 10: Schematic of High Performance 2-4 Decoder

Figure 81: Waveform of High Performance 2-4 decoder

ISSN: 2455-7838(Online)

# EPRA International Journal of Research and Development (IJRD)

Volume: 5 | Issue: 2 | February 2020

- Peer Reviewed Journal

Figure 92: Schematic of High performance

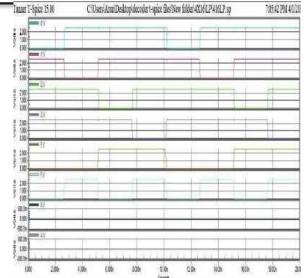

Figure 15: Waveform of CMOS 4-16 Decoder

Figure 13: Waveform of High performance Inverter

Figure 14: Schematic of CMOS 4-16 Decoder

Figure 17: Waveform of LP

## ISSN: 2455-7838(Online)

### EPRA International Journal of Research and Development (IJRD)

Volume: 5 | Issue: 2 | February 2020

- Peer Reviewed Journal

Figure 18: Schematic of LPI

Figure 21: Waveform of HPI

| 2-4 Decoder at 2GHz                                                                             |                                           |                                                            |                                                     |                                                            |                                             |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|---------------------------------------------|--|--|--|--|--|--|--|

|                                                                                                 | CMO                                       | 2-4                                                        | 2-4                                                 | 2-4                                                        | 2-4                                         |  |  |  |  |  |  |  |

| 0.8V                                                                                            | S                                         | HP                                                         | HPI                                                 | LP                                                         | LPI                                         |  |  |  |  |  |  |  |

| Power                                                                                           |                                           |                                                            |                                                     |                                                            |                                             |  |  |  |  |  |  |  |

| *10^-7                                                                                          | 4.56                                      | 1.48                                                       | 5.75                                                | 1.5                                                        | 1.81                                        |  |  |  |  |  |  |  |

| Delay*10^-                                                                                      |                                           |                                                            |                                                     |                                                            |                                             |  |  |  |  |  |  |  |

| 9                                                                                               | -0.39                                     |                                                            | failed                                              | -0.47                                                      | 1.06                                        |  |  |  |  |  |  |  |

|                                                                                                 | CMO                                       |                                                            | 2-4                                                 | 2-4                                                        | 2-4                                         |  |  |  |  |  |  |  |

| 1V                                                                                              | S                                         | HP                                                         | HPI                                                 | LP                                                         | LPI                                         |  |  |  |  |  |  |  |

| Power                                                                                           |                                           |                                                            |                                                     |                                                            |                                             |  |  |  |  |  |  |  |

| *10^-7                                                                                          | 6.83                                      | 1.81                                                       | 13.72                                               | 1.78                                                       | 2.34                                        |  |  |  |  |  |  |  |

| Delay*10^-                                                                                      |                                           |                                                            |                                                     |                                                            |                                             |  |  |  |  |  |  |  |

| 9                                                                                               | -0.43                                     |                                                            | 0.069                                               | -0.47                                                      | 1.05                                        |  |  |  |  |  |  |  |

| 4 277                                                                                           | CMO                                       |                                                            | 2-4                                                 | 2-4<br>LP                                                  | 2-4                                         |  |  |  |  |  |  |  |

| 1.2V                                                                                            | S                                         | HP                                                         | HPI                                                 | LP                                                         | LPI                                         |  |  |  |  |  |  |  |

| Power<br>*10^-7                                                                                 | 10.27                                     | 7 2.65                                                     | 39.85                                               | 2.58                                                       | 3.54                                        |  |  |  |  |  |  |  |

| Delay*10^-                                                                                      |                                           | 2.03                                                       | 39.03                                               | 2.30                                                       | 3.34                                        |  |  |  |  |  |  |  |

| 9                                                                                               | -0.44                                     | -0.47                                                      | failed                                              | -0.47                                                      | 1.04                                        |  |  |  |  |  |  |  |

|                                                                                                 | 0.1                                       | 0.17                                                       |                                                     |                                                            |                                             |  |  |  |  |  |  |  |

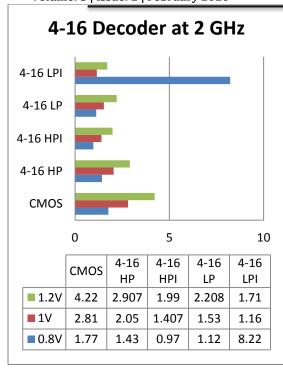

|                                                                                                 |                                           |                                                            |                                                     |                                                            | 4-16 Decoder at 2 GHz                       |  |  |  |  |  |  |  |

|                                                                                                 | CNAO                                      |                                                            |                                                     |                                                            |                                             |  |  |  |  |  |  |  |

| 0.077                                                                                           | СМО                                       | 4-16                                                       | 4-16                                                | 4-16                                                       | 4-16                                        |  |  |  |  |  |  |  |

| 0.8V                                                                                            | S                                         | 4-16<br>HP                                                 | 4-16<br>HPI                                         | 4-16<br>LP                                                 | 4-16<br>LPI                                 |  |  |  |  |  |  |  |

| Power                                                                                           | S                                         | HP                                                         | HPI                                                 | LP                                                         | LPI                                         |  |  |  |  |  |  |  |

| Power<br>*10^-6                                                                                 |                                           |                                                            | _                                                   | -                                                          |                                             |  |  |  |  |  |  |  |

| Power<br>*10^-6<br>Delay*10                                                                     | S<br>1.77                                 | HP<br>1.43                                                 | <b>HPI</b> 0.97                                     | <b>LP</b> 1.12                                             | <b>LPI</b> 8.22                             |  |  |  |  |  |  |  |

| Power<br>*10^-6                                                                                 | \$ 1.77 -0.3                              | 1.43<br>-0.43                                              | 0.97<br>1.21                                        | 1.12<br>-0.93                                              | 8.22<br>4.24                                |  |  |  |  |  |  |  |

| Power<br>*10^-6<br>Delay*10<br>^-9                                                              | S<br>1.77<br>-0.3<br>CMO                  | 1.43<br>-0.43<br><b>4-16</b>                               | 0.97<br>1.21<br>4-16                                | 1.12<br>-0.93<br><b>4-16</b>                               | 8.22<br>4.24<br><b>4-16</b>                 |  |  |  |  |  |  |  |

| Power<br>*10^-6<br>Delay*10<br>^-9                                                              | \$ 1.77 -0.3                              | 1.43<br>-0.43                                              | 0.97<br>1.21                                        | 1.12<br>-0.93                                              | 8.22<br>4.24                                |  |  |  |  |  |  |  |

| Power<br>*10^-6<br>Delay*10<br>^-9                                                              | S<br>1.77<br>-0.3<br>CMO<br>S             | 1.43<br>-0.43<br>4-16<br>HP                                | 0.97<br>1.21<br>4-16<br>HPI                         | 1.12<br>-0.93<br>4-16<br>LP                                | 8.22<br>4.24<br>4-16<br>LPI                 |  |  |  |  |  |  |  |

| Power<br>*10^-6<br>Delay*10<br>^-9<br>1V<br>Power<br>*10^-6                                     | S<br>1.77<br>-0.3<br>CMO                  | 1.43<br>-0.43<br><b>4-16</b>                               | 0.97<br>1.21<br>4-16                                | 1.12<br>-0.93<br><b>4-16</b>                               | 8.22<br>4.24<br><b>4-16</b>                 |  |  |  |  |  |  |  |

| Power<br>*10^-6<br>Delay*10<br>^-9                                                              | S<br>1.77<br>-0.3<br>CMO<br>S             | 1.43<br>-0.43<br>4-16<br>HP                                | 1.21<br>4-16<br>HPI<br>1.407                        | 1.12<br>-0.93<br>4-16<br>LP                                | 8.22<br>4.24<br>4-16<br>LPI                 |  |  |  |  |  |  |  |

| Power<br>*10^-6<br>Delay*10<br>^-9<br>1V<br>Power<br>*10^-6<br>Delay*10                         | -0.3<br>CMO<br>S                          | 1.43<br>-0.43<br>4-16<br>HP                                | 0.97<br>1.21<br>4-16<br>HPI                         | 1.12<br>-0.93<br>4-16<br>LP                                | 8.22<br>4.24<br>4-16<br>LPI<br>1.16         |  |  |  |  |  |  |  |

| Power<br>*10^-6<br>Delay*10<br>^-9<br>1V<br>Power<br>*10^-6<br>Delay*10                         | \$ 1.77 -0.3 CMO \$ 2.81                  | 1.43<br>-0.43<br>4-16<br>HP<br>2.05                        | 1.21<br>4-16<br>HPI<br>1.407                        | 1.12<br>-0.93<br>4-16<br>LP<br>1.53                        | 8.22<br>4.24<br>4-16<br>LPI<br>1.16<br>4.13 |  |  |  |  |  |  |  |

| Power<br>*10^-6<br>Delay*10<br>^-9<br>1V<br>Power<br>*10^-6<br>Delay*10<br>^-9                  | 1.77<br>-0.3<br>CMO<br>S<br>2.81<br>-0.39 | HP  1.43  -0.43  4-16 HP  2.05  -0.44  4-16                | 1.21<br>4-16<br>HPI<br>1.407<br>1.11<br>4-16        | 1.12<br>-0.93<br>4-16<br>LP<br>1.53<br>-0.44<br>4-16       | 4.24<br>4-16<br>LPI<br>1.16<br>4.13<br>4-16 |  |  |  |  |  |  |  |

| Power<br>*10^-6<br>Delay*10<br>^-9<br>1V<br>Power<br>*10^-6<br>Delay*10<br>^-9                  | 1.77<br>-0.3<br>CMO<br>S<br>2.81<br>-0.39 | HP  1.43  -0.43  4-16 HP  2.05  -0.44  4-16                | 1.21<br>4-16<br>HPI<br>1.407<br>1.11<br>4-16        | 1.12<br>-0.93<br>4-16<br>LP<br>1.53<br>-0.44<br>4-16       | 4.24<br>4-16<br>LPI<br>1.16<br>4.13<br>4-16 |  |  |  |  |  |  |  |

| Power<br>*10^-6<br>Delay*10<br>^-9<br>1V<br>Power<br>*10^-6<br>Delay*10<br>^-9<br>1.2V<br>Power | \$ 1.77 -0.3 CMO \$ 2.81 -0.39 CMO \$ \$  | 1.43<br>-0.43<br>4-16<br>HP<br>2.05<br>-0.44<br>4-16<br>HP | 1.21<br>4-16<br>HPI<br>1.407<br>1.11<br>4-16<br>HPI | 1.12<br>-0.93<br>4-16<br>LP<br>1.53<br>-0.44<br>4-16<br>LP | 4.24 4-16 LPI 1.16 4.13 4-16 LPI            |  |  |  |  |  |  |  |

# EPRA International Journal of Research and Development (IJRD)

Volume: 5 | Issue: 2 | February 2020

- Peer Reviewed Journal

ISSN: 2455-7838(Online)

| Table 4: Decoders at 1 GHz |       |       |        |       |       |  |

|----------------------------|-------|-------|--------|-------|-------|--|

| 2-4 Decoder at 1GHz        |       |       |        |       |       |  |

|                            | 2-4   | 2-4   |        |       |       |  |

| 0.8V                       | S     | HP    | HPI    | LP    | LPI   |  |

| Power                      |       |       |        |       |       |  |

| *10^-7                     | 4.59  | 1.5   | 12.68  | 1.5   | 1.83  |  |

| Delay*10^-                 |       |       |        |       |       |  |

| 9                          | -0.89 | -0.97 | 0.2    | -97   | 2.06  |  |

|                            | CMO   | 2-4   | 2-4    | 2-4   | 2-4   |  |

| 1V                         | S     | HP    | HPI    | LP    | LPI   |  |

| Power                      |       |       |        |       |       |  |

| *10^-7                     | 6.91  | 1.46  | 9.41   | 1.47  | 1.996 |  |

| Delay*10^-                 |       |       |        |       |       |  |

| 9                          | -0.93 | -1.97 | 0.22   | -1.97 | 4.05  |  |

|                            | CMO   | 2-4   | 2-4    | 2-4   | 2-4   |  |

| 1.2V                       | S     | HP    | HPI    | LP    | LPI   |  |

| Power                      |       |       |        |       |       |  |

| *10^-7                     | 8.36  | 2.15  | 50.65  | 2.11  | 2.98  |  |

| Delay*10^-                 |       |       |        |       |       |  |

| 9                          | -1.94 | -1.97 | failed | -1.97 | 4.04  |  |

| 4-16 Decoder at 500MHz |                   |        |        |        |       |

|------------------------|-------------------|--------|--------|--------|-------|

|                        | CM 4-16 4-16 4-16 |        |        |        |       |

| 0.8V                   | OS                | HP     | HPI    | LP     | LPI   |

| Power                  |                   |        |        |        |       |

| *10^-7                 | 0.144             | 0.119  | 8.105  | 9.233  | 8.22  |

| Delay*                 | -                 |        |        |        |       |

| 10^-9                  | 1.807             | -1.932 | 4.213  | -1.932 | 4.249 |

|                        | CM                | 4-16   | 4-16   | 4-16   | 4-16  |

| 1V                     | OS                | HP     | HPI    | LP     | LPI   |

| Power                  |                   |        |        |        |       |

| *10^-6                 | 2.78              | 1.15   | 1.073  | 91.8   | 1.167 |

| Delay*                 |                   |        |        |        |       |

| 10^-9                  | 0.008             | -0.05  | failed | -0.05  | 4.13  |

|                        | CM                | 4-16   | 4-16   | 4-16   | 4-16  |

| 1.2V                   | OS                | HP     | HPI    | LP     | LPI   |

| Power                  |                   |        |        |        |       |

| *10^-6                 | 3.45              | 2.39   | 1.63   | 1.807  | 1.71  |

| Delay*                 |                   |        |        |        | _     |

| 10^-9                  | -1.91             | -1.95  | 4.09   | -1.95  | 4.102 |

| 4-16 Decoder at 1GHz |        |        |        |        |       |

|----------------------|--------|--------|--------|--------|-------|

|                      | CM     | 4-16   | 4-16   | 4-16   | 4-16  |

| 0.8V                 | OS     | HP     | HPI    | LP     | LPI   |

| Power                |        |        |        |        |       |

| *10^-7               | 5.92   | 5.11   | 4.18   | 3.82   | 8.22  |

| Delay*1              |        |        |        |        |       |

| 0^-9                 | 0.18   | 0.09   | failed | 0.09   | 4.24  |

|                      | CM     | 4-16   | 4-16   | 4-16   | 4-16  |

| 1V                   | OS     | HP     | HPI    | LP     | LPI   |

| Power                |        |        |        |        |       |

| *10^-6               | 2.78   | 1.15   | 1.07   | 0.91   | 1.16  |

| Delay*1              |        |        |        |        |       |

| 0^-9                 | 0.008  | -0.05  | failed | -0.05  | 4.13  |

|                      | CM     | 4-16   | 4-16   | 4-16   | 4-16  |

| 1.2V                 | os     | HP     | HPI    | LP     | LPI   |

| Power                |        |        |        |        |       |

| *10^-6               | 4.18   | 2.16   | 1.85   | 1.92   | 1.71  |

| Delay*1              |        |        |        |        |       |

| 0^-9                 | -0.016 | -0.055 | 0.29   | -0.055 | 4.102 |

| 2-4 Decoder at 2 GHz |        |       |        |            |        |         |  |  |

|----------------------|--------|-------|--------|------------|--------|---------|--|--|

| 2                    | -4 LPI |       |        |            |        |         |  |  |

| 2                    | 2-4 LP |       |        |            |        |         |  |  |

| 2-                   | 4 HPI  |       |        |            |        |         |  |  |

| 2                    | -4 HP  |       |        |            |        |         |  |  |

| C                    | CMOS   |       |        |            |        |         |  |  |

|                      |        | 0     | 20     |            | 40     | 60      |  |  |

|                      |        | CMOS  | 2-4 HP | 2-4<br>HPI | 2-4 LP | 2-4 LPI |  |  |

|                      | ■ 1.2V | 10.27 | 2.65   | 39.85      | 2.58   | 3.54    |  |  |

|                      | ■ 1V   | 6.83  | 1.81   | 13.72      | 1.78   | 2.34    |  |  |

|                      | ■ 0.8V | 4.56  | 1.48   | 5.75       | 1.5    | 1.81    |  |  |

| Table 5: Decoders a | t 500MHz | 1 |

|---------------------|----------|---|

|---------------------|----------|---|

|           | 2-4 Decoder at 500MHz |       |        |       |     |  |  |

|-----------|-----------------------|-------|--------|-------|-----|--|--|

|           |                       |       |        |       | 2-4 |  |  |

|           | CM                    | 2-4   | 2-4    | 2-4   | LP  |  |  |

| 0.8V      | OS                    | HP    | HPI    | LP    | I   |  |  |

| Power     |                       |       |        |       | 1.5 |  |  |

| *10^-7    | 3.73                  | 1.26  | 2.91   | 1.27  | 1   |  |  |

| Delay*10^ |                       |       |        |       | 4.0 |  |  |

| -9        | -1.89                 | -1.97 | 0.005  | -1.97 | 6   |  |  |

|           |                       |       |        |       | 2-4 |  |  |

|           | CM                    | 2-4   | 2-4    | 2-4   | LP  |  |  |

| 1V        | OS                    | HP    | HPI    | LP    | I   |  |  |

| Power     |                       |       |        |       | 1.9 |  |  |

| *10^-7    | 5.58                  | 1.46  | 9.41   | 1.47  | 9   |  |  |

| Delay*10^ |                       |       |        |       | 4.0 |  |  |

| -9        | -1.93                 | -1.97 | 22.46  | -1.97 | 5   |  |  |

|           |                       |       |        |       | 2-4 |  |  |

|           | CM                    | 2-4   | 2-4    | 2-4   | LP  |  |  |

| 1.2V      | OS                    | HP    | HPI    | LP    | I   |  |  |

| Power     |                       |       |        |       | 2.9 |  |  |

| *10^-7    | 8.36                  | 2.15  | 0.506  | 2.11  | 8   |  |  |

| Delay*10^ |                       |       |        |       | 4.0 |  |  |

| -9        | -1.94                 | -1.97 | failed | -1.97 | 4   |  |  |

Figure 102: Average Power of 2-4 Decoder in Micro Watts

### EPRA International Journal of Research and Development (IJRD)

Volume: 5 | Issue: 2 | February 2020

- Peer Reviewed Journal

ISSN: 2455-7838(Online)

Figure 23: Average Power of 4-16 Decoder in Micro Watts

#### V. **CONCLUSION**

This brief has introduced an efficient mixedlogic design for decoder circuits, combining TGL, DVL and static CMOS. By using this methodology, we developed four new 2-4 line decoder topologies, namely 2-4LP, 2-4LPI, 2-4HP and 2-4HPI, which offer reduced transistor count and improved power delay performance in relation to conventional CMOS decoders. Furthermore, four new 4-16 line decoder topologies were presented, namely 4-16LP, 4-16LPI, 4-16HP and 4-16HPI, realized by using the mixed-logic 2-4 decoders as pre decoding circuits, combined with post decoders implemented in static CMOS to provide driving capability. A variety of comparative spice simulations was performed at 32 nm, verifying, in most cases, a definite advantage in favor of the proposed designs.

A decoder consumes almost 30% of the total power in a memory circuit and hence it becomes mandatory to optimize a decoder circuit in the memory architecture. The main feature of the present work is to optimize the decoder designs in order to achieve better speed and power performance. This work can be extended by using various mixed design styles like DVL, gating technique etc. in this we can obtain better results than CMOS logic where the power consumption and transistor count can be reduced. By this way can obtain less power consumption and high

performance operation when compared to CMOS logic design technique.

We can use these decoders in the applications where low power consumption and decoding is necessary such as data multiplexing, 7 segment display and memory address decoding.

### REFERRENCES

- 1. N. H. E. Weste and D. M. Harris, CMOS VLSI Design, a Circuits and Systems Perspective, 4th ed. Boston, MA, USA: Addison-Wesley,

- 2. R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," IEEE J. Solid State Circuits, vol. 32, no. 7, pp. 1079-1090, Jul. 1997.

- 3. K. Yano et al., "A 3.8-ns CMOS  $16 \times 16$ -b multiplier using complementary pass-transistor logic," IEEE J. Solid-State Circuits, vol. 25, no. 2, pp. 388-393, Apr. 1990.

- M. Suzuki et al., "A 1.5 ns 32b CMOS ALU in double pass-transistor logic," in Proc. IEEE Int. Solid-State Circuits Conf., 1993, pp. 90-

- X. Wu, "Theory of transmission switches and its application to design of CMOS digital circuits," Int. J. Circuit Theory Appl., vol. 20, no. 4, pp. 349-356, 1992.

- V. G. Oklobdzija and B. Duchene, "Passtransistor dual value logic for low-power CMOS," in Proc. Int. Symp. VLSI Technol., 1995,pp. 341-344.

- 7. M. A. Turi and J. G. Delgado-Frias, "Decreasing energy consumption in address decoders by means of selective precharge schemes, "Microelectron. J., vol. 40, no. 11, pp. 1590-1600, 2009.

- V. Bhatnagar, A. Chandani, and S. Pandey, "Optimization of row decoder for 128 × 128 6T SRAMs," in Proc. IEEE Int. Conf. VLSI-SATA, 2015, pp. 1–4.

- A. K. Mishra, D. P. Acharya, and P. K. Patra, "Novel design technique of address decoder for SRAM," Proc. IEEE ICACCCT, 2014, pp. 1032–1035.

- 10. D. Markovi'c, B. Nikoli'c, and V. G. Oklobdžija, "A general method in synthesis of pass-transistor circuits," Microelectron. J., vol. 31, pp. 991–998, 2000.

- 11. [Online]. Available: http://ptm.asu.edu/

- 12. N. Lotze and Y. Manoli, "A 62 mV 0.13 µm CMOS standard-cellbased design technique using Schmitt-trigger logic," IEEE J. Solid State Circuits, vol. 47, no. 1, pp. 47-60, Jan. 2012.