SJIF Impact Factor: 6.260| ISI I.F.Value:1.241| Journal DOI: 10.36713/epra2016 ISSN: 2455-7838(Online)

## **EPRA International Journal of Research and Development (IJRD)**

Volume: 5 | Issue: 4 | April 2020 - Peer Reviewed Journal

# FOUR SWITCH THREE PHASE SEPIC INVERTER WITH FRONT END BOOST CONVERTER

## Raheema V<sup>1</sup>

Mtech student<sup>1</sup>, Power Electronics and drives, Department of Electrical and Electronics Engineering, MEA Engineering College, Vengoor P.O, Perinthalmanna, Malappuram, Kerala-679325

## Fasil T. Mohammed <sup>2</sup>

Lecturer<sup>2</sup>, Department of Mechanical Skills, Jubail Technical Institute, Royal Commission of Jubail, Jubail Industrial city-31961, Jubail-Kingdom of Saudi Arabia.

Article DOI: https://doi.org/10.36713/epra4305

#### **ABSTRACT**

In this paper, four switch sepic inverter with front end boost converter capable of producing quality three phase ac output is explained. Proposed topology is an advanced one when comparing with conventional topologies. Converter offer a design for the inverter with the combination of single-ended primary-inductance, which can obtain higher phase voltages compared to conventional four switch and six switch three phase inverters. A differential arrangement of SEPIC enables to obtained three phase balanced output voltage with only four switches. The output voltage is pure sinusoidal without the help of external filter. This proposed inverter is designed to reduce the cost, complexity and switching losses. It also improves the efficiency and reduces the harmonic distortion. Here the output of the inverters are connected deferentially across the load. The line voltage can not exceed the full value of the input dc voltage, for avoiding this a dc - dc boost converter is placed in the front end of the four switch sepic inverter, thus producing the required output voltage along with the sinusoidal nature. Due to this features, the inverter can be used for the grid integration and pv based power extraction. Proposed topology is operated in both current control algorithm and a modified sine pwm control technique. In this paper it is based on the novel sine pwm control technique. The topology is analysed, simulated using MATLAB/SIMULINK and also a prototype is accomplished to verify the feasibility of the proposed topology.

Index Terms—Three-phase inverter, Bi directionl sinlge ended primary inductance converter, Novel sin pwm control, DC-DC boost converter,

### EPRA International Journal of Research and Development (IJRD)

Volume: 5 | Issue: 4 | April 2020 - Peer Reviewed Journal

#### **INTRODUCTION**

The conventional six-switch three-phase (SSTP) voltage source inverter(VSI) has found widespread industrial applications in different forms such as motor drives, renewable energy conversion systems, and active power filters, also, in some low power range applications. This novel design showing, this is possible to apply a three phase with at best four switches.

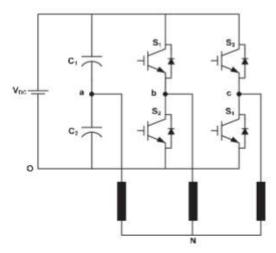

Figure 1. Conventional FSTP inverter.

In three phase inverter with four switch ,two load outputs are connected to the inverter leg and the remaining load is connected to the input side at a middle point of the capacitor C<sub>C</sub> and C<sub>2</sub> as shown in figure 1. Comparing with this SSTP inverters four switch three phase inverters have some more advantages such as reducing number of switches and also reduces the switching losses. And also reducing one entire leg we can also reduce the interface circuit. How ever there also some disadvantages for the conventional FSTP inverter ,it only performs for DC-AC buck operation and also the peak output phase voltage can be reduced by  $V_{dc}/2\sqrt{3}$ , where it is  $V_{dc}/2$  in SSTP. So that for avoiding this problems insert a boost converter(DC-DC) between the input side and the three phase inverter. So that we can improve the rate of the phase voltage than a normal converters.

Here introducing a design for the four switch three phase inverter topology followed by the SEPIC converter with a boost converter. The SEPIC converter provides both buck and boost operation. But here only used the buck operations. Although this inverter can rise a phase voltage comparing with the conventional four switch three phase voltage source inverter than two. Another feature of the proposed SEPIC inverter with boost converter is getting a pure sinusoidal output

voltage waveform and also avoiding the filter requirements at the output stage with the help of a modified sine pwm control.

#### LITERATURE REVIEW

After reviewing the Literature, it can be concluded that only limited inverters are performed in this area.[1] In single phase SEPIC inverter topology, employs only two switches to achieve DC-AC conversion with a full utilization of the DC input voltage (i.e. the output AC voltage peak is ranged from 0 to VDC). In addition, it generates a pure sinusoidal wave at output terminals. Unlike conventional VSI, the single phase SEPIC inverter has no vital need to insert a dead band between the two switches, which significantly reduces the output waveform distortion and gain non-linearity. But this converter is applicable only in single phase. [2] Some research efforts have been directed to develop inverter topologies that can achieve the aforementioned goal. The results obtained showed that it is possible to implement a three-phase sepic inverter with only four switches This makes it very robust and serves major reason to be used widely in industries . This sepic based four switch three phase inverter has got many advantages over conventional four switch three phase inverters, like capacitor voltage balancing issue and maximum dc bus voltage utilization. The switching pulses are generated with the help of modified sine pwm control technique. [3] Different Control Options For The B4 Inverters are listed, Two-Level Current Control, Feeding a Three-Phase Load From Two Voltage Sources, Phase Asymmetric Control Of B4 Bridge. [4]Micro-grid research has received the prime interest in the domain of power system research due to the efforts of different governmental agencies to reduce the consumption of fossil fuel . Renewable energy is also penetrating in the modern power grids to reduce the global carbon footprints. In the recent past various sophisticated control methodologies as well as different high end converter/inverter topologies are investigated to ensure efficient operation of the micro-grid systems. Three-phase micro-grids are also receiving significant research interest due to the high level power transfer capability of the overall power network.

#### PROPOSED SYSTEM

This describes in detail about the circuit topology of the proposed four switch three phase sepic inverter with front end boost converter. This sepic based four switch three phase inverter has got many advantages over conventional four switch three phase inverters ,like capacitor voltage balancing issue and maximum dc bus voltage utilization. The switching pulses are generated with the help of modified sine pwm control

SJIF Impact Factor: 6,260| ISI I.F.Value:1,241| Journal DOI: 10.36713/epra2016 ISSN: 2455-7838(Online)

## **EPRA International Journal of Research and Development (IJRD)**

Volume: 5 | Issue: 4 | April 2020 - Peer Reviewed Journal

technique.

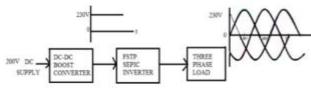

Figure 3 . Block diagram of proposed sytem

The proposed system consists of DC-DC boost converter, FSTP SEPIC inverter and a three phase load is shown in figure 2.A200V is given as the input side and the boost converter boost up the value up to 250V. The phase voltage across the load becomes boost up and around 230V.In conventional FSTP SEPIC inverter when giving an input of 200V, the output becomes 150V.So in order to improves the phase voltage, inserting a boost converter in between the dc input side and the four switch three phase sepic inverter.

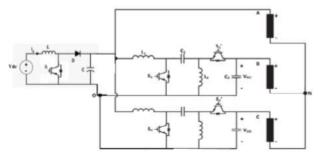

Figure 2 . Circuit diagram of FSTP SEPIC inverter with front end boost converter

The detailed configuration of FSTP SEPIC inverter with front end boost converter is shown in figure 2. The inverter consists of two SEPIC converters, and achieves DC- AC conversion. And at the front end of the input side, a boost converter is placed for achieving DC- DC conversion and also increasing the input voltage.

## FEATERS OF PROPOSED INVERTER TOPOLOGY

- Get sinusoidal three phase output voltage without the help of filter components.

- THD value of the proposed topology is very much improves when comparing with the conventional topologies.

- The voltage gain also increase with the help of front end boost converter.

- Proposed topology requires only four switches in the inverting stage and one for boosting stage.

Required number of switches much reduced without affecting the quality of output voltage.

## CONTROL STRATEGY AND DESIGN OF FSTP SEPIC INVERTER

#### • MODIFIED SINE PWM CONTROL

The term SPWM stands for "Sinusoidal pulse width modulation" is a technique of pulse width modulation used in inverters. An inverter generates an output of AC voltage from an input of DC with the help of switching circuits to reproduce a sine wave by generating one or more square pulses of voltage per half cycle. If the size of the pulses is adjusted, the output is said to be pulse width modulated. With this modulation, some pulses are produced per half cycle. The pulses close to the ends of the half cycle are constantly narrower than the pulses close to the centre of the half cycle such that the pulse widths are comparative to the equivalent amplitude of a sine wave at that part of the cycle. To change the efficient output voltage, the widths of all pulses are amplified or reduced while keeping the sinusoidal proportionality. With PWM (pulse width modulation), only the on-time of the pulses are changed during the amplitudes.

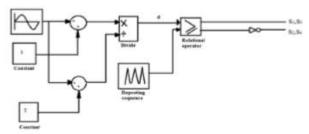

Figure 4. Block diagram

If we take the duty ratio as,

$d = Dsin(\omega t)$

Where D = 1, we get a non linear output like,

$$V_o = (D\sin\omega t) / (1-D\sin\omega t) *V_{in}$$

To make the input output relation is sinusoidal voltage with sine nature, the duty ratio is change to,

$d = (1 + \sin\omega t) / (2 + \sin\omega t)$

we get the sinusoidal output as,

$$d / (1-d) = (1 + \sin \omega t)$$

$$V_{out} = (1 + \sin \omega t) * V_{in}$$

In this subsection, the previously deduced equations are used to select the appropriate values of the components used in the proposed SEPIC inverter. The design specifications of the proposed FSTP SEPIC inverter are as follows:

- 1) Input voltage: 200 VDC.

- 2) Peak output line voltage: 230VAC.

- 3) Output frequency: 50 Hz.

- 4) Switching frequency: 20 kHz.

SJIF Impact Factor: 6.260| ISI I.F.Value:1.241| Journal DOI: 10.36713/epra2016 ISSN: 2455-7838(Online)

## EPRA International Journal of Research and Development (IJRD)

Volume: 5 | Issue: 4 | April 2020 - Peer Reviewed Journal

5) Rated current:Im = 4A (Load:  $25 \Omega$  series with 1 mH)

#### SIMULATION ANALYSIS AND RESULT

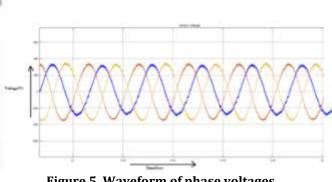

Figure 5. Waveform of phase voltages

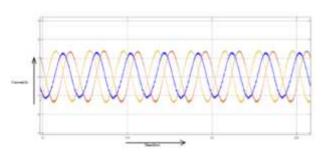

Figure 6. Waveform of load currents

Figure 5 and 6 shows the wave form of load current across the load. The inverters are connected differentialy across the load, here load is resistive in nature and having the value of  $300\Omega$ . The peak value of output voltage is around 230V.So the load current become 230/300 =0.766A.

**Table 1..Simulation Parameters Of Three Phase SEPIC Inverter**

| SI.No. | Parameters                          | Value       |

|--------|-------------------------------------|-------------|

| 1      | Input voltage, V <sub>in</sub>      | 200V        |

| 2      | Output voltage, Vout                | 230V        |

| 3      | Switching frequency ,f <sub>s</sub> | 20kHz       |

| 4      | Inductor,L <sub>1B</sub>            | 6.7mH       |

| 5      | Inductor,L <sub>2B</sub>            | 2.26mH      |

| 6      | Inductor,L <sub>1C</sub>            | 7mH         |

| 7      | Inductor ,L <sub>2C</sub>           | 2.36mH      |

| 8      | Capacitor,C <sub>1B</sub>           | $10.6\mu F$ |

| 9      | Capacitor, C <sub>2B</sub>          | $2.8\mu F$  |

| 10     | Capacitor,C <sub>1C</sub>           | $10.3\mu F$ |

| 11     | Capacitor, C <sub>2C</sub>          | $2.8\mu F$  |

| 12     | Resistive load                      | $200\Omega$ |

**Table 2...Simulation Parameters For Boost Converter**

| SI.No. | Parameters                          | Value       |

|--------|-------------------------------------|-------------|

| 1      | Input voltage, V <sub>in</sub>      | 200V        |

| 2      | Switching frequency ,f <sub>s</sub> | 20kHz       |

| 3      | Inductor,L <sub>1</sub>             | 6.7mH       |

| 4      | Capacitor,C <sub>1</sub>            | $10.6\mu F$ |

| 12     | Resistive load                      | $200\Omega$ |

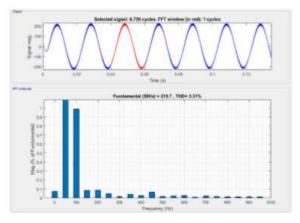

Figure 7.THD calculation of proposed inverter. From the measurement it is clear, the value of THD is about 3.31%.

Figure 8. Complete setup of the hardware

#### **CONCLUSION**

Four switch three phase sepic inverter with front end boost converter is proposed in this paper. The inverter can produce three-phase output voltage with pure sinusoidal nature with minimum number of switches .Unlike other three phase inverters ,proposed inverter dose not need any output filter. Also it does not suffer from the problems of voltage fluctuation across the DC link split-capacitors, as the third

### EPRA International Journal of Research and Development (IJRD)

Volume: 5 | Issue: 4 | April 2020 - Peer Reviewed Journal

phase load current is directly drawn from the DC source without circulation in any passive component. The proposed converter topology has following features, THD value of the proposed topology is very much improved when comparing with the conventional topologies.

- The voltage gain is also increased with the help of front end boost converter.

- Proposed topology requires only four switches in the inverting stage and one for boosting stage.

- The number of switches required is reduced without affecting the quality of output voltage.

#### REFERENCES

- 1. W. Yu, J. Lai, H. Qian, and C. Hutchens, "A reduced switch-count single phase sepic-based inverter," IEEE Trans. Power Electron, vol. 26, no. 4, pp. 1253—

- 2. J. Anderson and F. Z. Peng, "A four-switch threephase sepic-based inverter,"

- 3. R. O. Caceres and I. Barbi, "A comparative investigation of a three-phase induction machine drive with a component minimized voltage-fed inverter under different control options," IEEE Trans. Power Electron, vol. 14, no. 4, pp. 134–141,

- 4. Y. Tang, Y. Bai, J. Kan and F. Xu, "A general pwm strategy for four-switch three-phase inverters," IEEE Trans. Power Electron, vol. 10, no. 8, pp. 1253–1260,2016.

- W. Yu, J. Lai, H. Qian, and C. HutchensP. W. Sun, C. Liu, J.-S. Lai, and C.-L. Chen, "Cascade dual buck inverter with phase-shift control," IEEE Trans. Power Electron, vol. 26, no. 4, pp. 1253–1260, 2011.

- 6. A. A. Khan, H. Cha, and H.-G. Kim, "Three-phase three-limb coupled in ductor for three-phase direct pwm ac-ac converters solving commutation problem," IEEE Trans. Power Electron, vol. 63, no. 4, pp. 189–209, 2016.

- 7. A. A. Khan, H. Cha, and H. F. Ahmed, "An improved single-phase direct pwm inverting buck-boost ac-ac converter," IEEE Trans. Power Electron, vol. 67,no. 4, pp. 5384–5393, 2011.

- 8. A. Khan, H. Cha, H. F. Ahmed, J. Kim and J. Cho, "A highly reliable and high efficiency quasi single-stage buck-boost inverter," IEEE Trans. Power Electron, vol. 10, no. 4, pp. 1253–1260, 2017.

- 9. A. A. Khan, "Position sensorless control for fourswitch three-phase brushless dc motor drives," IEEE Trans. Power Electron, vol. 10, no. 4, p. 1200=1243, 2013.

- M. Mahdavi, "Bridgeless sepic pfc rectifier with reduced components and conduction losses," IEEE Trans. Power Electron, vol. 10, no. 4, p. 1200=1243, 2013.

- 11. Mohamadian, "A novel reduced switch count single-phase to three-phase ac/ac converter," in IEEE Trans. Power Electron, vol. 10. IEEE, 2012.

- 12. Caceres, "A boost dc-ac converter: analysis, design, and experimentation," IEEE Trans. Power Electron, vol. 10, no. 4, p. 1200=1243, 2012.