#### **Chief Editor** Dr. A. Singaraj, M.A., M.Phil., Ph.D. **Editor** Mrs.M.Josephin Immaculate Ruba **EDITORIAL ADVISORS** 1. Prof. Dr.Said I.Shalaby, MD, Ph.D. **Professor & Vice President Tropical Medicine**, Hepatology & Gastroenterology, NRC, Academy of Scientific Research and Technology, Cairo, Egypt. 2. Dr. Mussie T. Tessema, Associate Professor, **Department of Business Administration,** Winona State University, MN, United States of America, 3. Dr. Mengsteab Tesfayohannes, Associate Professor, Department of Management, Sigmund Weis School of Business, Susquehanna University, Selinsgrove, PENN, United States of America, 4. Dr. Ahmed Sebihi **Associate Professor** Islamic Culture and Social Sciences (ICSS), Department of General Education (DGE), Gulf Medical University (GMU), UAE. 5. Dr. Anne Maduka, Assistant Professor, **Department of Economics**, Anambra State University, Igbariam Campus, Nigeria. 6. Dr. D.K. Awasthi, M.SC., Ph.D. **Associate Professor Department of Chemistry**, Sri J.N.P.G. College, Charbagh, Lucknow, Uttar Pradesh. India 7. Dr. Tirtharaj Bhoi, M.A, Ph.D, Assistant Professor. School of Social Science. University of Jammu, Jammu, Jammu & Kashmir, India. 8. Dr. Pradeep Kumar Choudhury, Assistant Professor. Institute for Studies in Industrial Development, An ICSSR Research Institute, New Delhi- 110070, India. 9. Dr. Gyanendra Awasthi, M.Sc., Ph.D., NET Associate Professor & HOD Department of Biochemistry, Dolphin (PG) Institute of Biomedical & Natural Sciences, Dehradun, Uttarakhand, India. 10. Dr. C. Satapathy, Director, Amity Humanity Foundation, Amity Business School, Bhubaneswar, Orissa, India.

ISSN (Online): 2455-7838 SJIF Impact Factor (2016): 4.144 UGC Approved Journal No: 48844

# EPRA International Journal of

# **Research & Development** (IJRD)

Monthly Peer Reviewed & Indexed International Online Journal

Volume:2, Issue:7, July 2017

UGC Approved Journal No: 48844ISSN: 2455-7838(Online)EPRA International Journal of Research and Development (IJRD)SJIF Impact Factor: 4.144Volume: 2 | Issue: 7 | July | 2017

# SINGLE PHASE SEVEN LEVEL PWM MULTILEVEL INVERTER WITH SELF VOLTAGE BALANCING CAPACITORS

Deenu.K<sup>1</sup>

<sup>1</sup>Applied Electronics,Dr.Mahalingam College Of Engineering And Technology,Coimbatore,India

# Kalaivani.M<sup>2</sup>

<sup>2</sup>Applied Electronics,Dr.Mahalingam College Of Engineering And Technology,Coimbatore,India)

#### ABSTRACT

The Multilevel inverter (MLI) are the preferred choice in industry for the application of medium and high power application. Though multilevel inverter has a number of favour and also has disadvantages in the way of achieving the higher <sup>levels</sup> because of using more amount of semiconductor devices. This may lean towards to increase the installation cost and area. Hence to overthrown this problem the new multilevel inverter is introduced with minimum number of power electronic components. The proposed method is appropriate for high power application with minimum quantity of devices. Phase disposition PWM technique is used for switching signal generation. The results are validated using MATLAB/Simulink and it is implemented in SPARTAN6 FPGA Kit.

**KEYWORDS**: Field Programmable Gate Array (FPGA), Multilevel Inverter (MLI), Phase Disposition Pulse Width Modulation;

#### **I.INTRODUCTION**

Now a days, multilevel inverters has drawn large interest from the diligence exhausting mediumvoltage and high power solicitations. Multilevel inverters generate many voltage levels. A preferred output voltage waveform can be symphonized from the multiple voltage levels with low bias, low switching frequency, higher competence, and lower voltage devices.Yet, it requires a huge quantity of circuit modules[1]-[5].In conservative multilevel inverters, a cascaded H-bridge multilevel inverter (CHB) is the solitary preferred choice to upsurge the amount of output voltage levels. However, the Hbridge cells by increasing the CHB, and it also increases power electronic devices [6]-[7]. The superlative elucidations to generate the highest yield of voltage stages by minimize the quantity of circuit apparatuses in a CHB is to use asymmetrical dc voltage [8]-[9]. The H converters which are coupled to the each phase inverter which is connected to the same DC link by scaling the source with the power of three. Conversely for up surging the voltage level, which increases the dc voltage source. The cascaded transformer is employed [10] with six floating power supplies are used to alleviate this problem. Due to the usage of cascaded transformer the system becomes hulky. To elude this difficulty, the proposed multilevel inverter engaging four floating power supplies are included[11].Yet to obtain independent dc voltage source, it also requires front end transformer so transformer less circuit topologies are introduced [12]-[18].In [12], a packed U-cell multilevel inverter topology stood introduced which has reduced amount of circuit components. Furthermore it also requires a bulky capacitor of 5000µF which hosts the high ripples. Multilevel inverters retaining bidirectional switches with serieslinked capacitors was announced in [13]-[14]. Hypothetically, by reducing the number of circuit components, they can achieve a huge amount of output voltage levels up 125 levels. To generate this a modular multilevel converter was proposed in [15]. It has a good modular characteristic; thus, it is flexible to extend to increasing the voltage stages. Nevertheless, by compared with other rival it surges the amount of hulking capacitors and switches. A multilevel inverter using series-connected dc voltage sources was recommended in [16]. It includes two stages one of them is a level-spawning stage and second stage is polarity generating part to lessen the switching losses. Yet, it flops to curtail the amount of dc voltage sources by increasing the output voltage stages. A multilevel inverter engaging switched series/parallel dc voltage sources was introduced in [17]. Despite it can growth the amount of output voltage stages, but the switching pattern is multifaceted, and it transmission fatalities will be high. A photovoltaic multilevel inverter using serieslinked capacitors was labouring in [18]. It do not clarify about the capacitor voltage balancing. The preceding tactics agreed in [12]-[18] uses seriesattached capacitors. This is beneficial to increase the output voltage stages and solves the capacitor voltage destabilizing problematic by minimising the number of independent dc voltage sources. In this manuscript, we introduce a compelling circuit arrangement of a multilevel inverter with a minimised amount of circuit apparatuses. It subsist of a single dc voltage source paralleled to series linked capacitors, two diodes, three switches for incorporating the output voltage levels, and an H-bridge cell. Here, we also propose a modified pulse width modulation (PWM) control strategy to solve the capacitor voltage destabilizing problem that arose in series connected capacitors. Then the validated output is counterfeit in MATLAB/Simulink and implemented in FPGA kit.

### 2. SEVEN LEVEL PWM INVERTER 2.1 Circuit Configuration

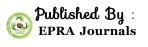

Fig. 1 shows a circuit arrangement of the 7- level PWM inverter. The 7-level PWM inverter take on single dc voltage source, which is branched by three series linked capacitors. Each capacitor voltage is equivalently branched to Vdc/3. Then, we can attain the 7- stages in the output voltage wave, i.e., Vdc, 2 Vdc/3, Vdc/3, 0, -Vdc/3, -2 Vdc/3, and -Vdc. The H-bridge cell includes switches (S1 ~S4) is used to regulate the polarity of the output voltage with the highest (or lowest) voltage level, i.e., Vdc (or -Vdc) and remaining voltage levels are generated by S5, S6, and S7.

Fig. 1. Circuit arrangement of the seven-level PWM inverter

#### 2.1.1 Generation of Output Voltage Levels

Level V<sub>dc</sub>. Three series connected capacitors deliveries energy to the output load. It discharges through the switches  $S_1$  and  $S_4$ . If an inductive load is used and the load current is streams in opposite direction, then the current streams over  $D_{S_1}$  and  $D_{S_4}$ , and it energies the capacitor mound.

Level  $2V_{dc}/3$ : Two capacitors voltage  $C_2$  and  $C_3$  supplies energy to the output load. It discharges over  $S_5$ ,  $D_1$ , and  $S_4$ . Here no current flows over during this switching state, when the direction of the load current is opposite. At this moment, the load current streams over  $D_{S_1}$  and  $D_{S_4}$ , and it energies the capacitor mound.

Level V<sub>dc</sub>/3: The bottom end capacitor ( $C_3$ ) supplies energy to the output load. It releases over  $D_{56}$ ,  $S_7$ ,  $D_1$ , and  $S_4$ . If the direction of the load current is reverse, the load current streams over  $D_2$ ,  $S_7$ ,  $D_{55}$ , and  $D_{54}$ .

Level 0: To make a zero level, two switching arrangements can be recognized. The voltage elimination is the elementary notion for generate a zero level. When S2 and S4 turn on concurrently, the output voltage becomes zero. The alternate scheme is to turn S1 and S3 on at the same time.

Level -Vdc/3: To generate a -Vdc/3 voltage level, the upper end capacitor (C1) carries energy to the output load.

*Level* -2 V dc/3: Two capacitors C1 and C2 carry charges to the output load. When the load current is opposite, it flows through DS2 and DS3.

Level –Vdc: Three series connected capacitors carries energy to the output load. If the direction of load current is reverse, the current streams over *DS*2 and *DS*3, and it charges the capacitor mound.

#### 2.1.2 General Switching Scheme

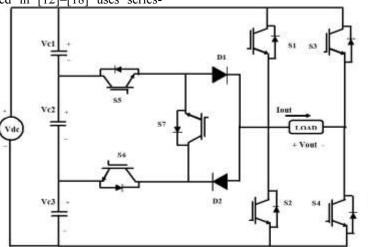

Fig. 2 shows switching pattern of general phase disposition technique for achieving the 7-level PWM inverter. It contains a reference and three carrier waves. The 3-carrier waves which have the same frequency and but dissimilar amplitudes [19], [20]. By paralleling the reference and each carrier wave, it generates the command signals (*Ca, Cb,* and *Cc*). One cycle of the reference voltage is divided into six modes according to the output voltage levels, and the corresponding period (*Pn*) for each mode is obtained by

Mode 1 :  $P1 = 0 < \omega t < \theta 1$  and  $P5 = \theta 4 < \omega t < \pi$  (1) Mode 2 :  $P2 = \theta 1 < \omega t < \theta 2$  and  $P4 = \theta 3 < \omega t < \theta 4$  (2) Mode 3 :  $P3 = \theta 2 < \omega t < \theta 3$  (3) Mode 4 :  $P6 = \pi < \omega t < \theta 5$  and  $P10 = \theta 8 < \omega t < 2\pi$  (4) Mode 5 :  $P7 = \theta 5 < \omega t < \theta 6$  and  $P9 = \theta 7 < \omega t < \theta 8$  (5) Mode 6 :  $P8 = \theta 6 < \omega t < \theta 7$ . (6)

The switching signals (*Sn*) are generated by the logical combination of *Ca*, *Cb*, *Cc*, and *Pn*. By setting the modulation index larger than 0.66 then determine the switching angles  $\theta n$  to generate period (*Pn*) of each mode for seven level. By using logical expressions AND, OR, and NOT, each switching signal is generated by

$S1 = \underline{Ca} \cdot (P6 + P10) + Cc \cdot P3$   $S2 = \underline{Ca} \cdot (P1 + P5) + Cc \cdot P8$  S3 = P6 + P7 + P8 + P9 + P10 Single Phase seven level PWM Multilevel Inverter with Self voltage balancing capacitors

$$S4 = P1 + P2 + P3 + P4 + P5$$

(10)

$$S5 = Cb \cdot (P2 + P4) + Cc \cdot P3$$

(11)

$$S6 = Cb \cdot (P7 + P9) + Cc \cdot P8$$

(12)

$$S7 = Ca \cdot (P1 + P5 + P6 + P10) + Cb \cdot (P2 + P4 + P7 + P9).$$

(13)

Table I shows switching angle  $\theta n$  affording to modulation ratio *Ma*. For generating the seven level a reference wave and 3- carrier waves are used. Therefore, modulation ratio *Ma* is calculated by

$$Ma = Am \tag{14}$$

where Ac is the amplitude of a carrier wave, and Am is the amplitude of a reference wave. Thus, the output voltage is calculated by

$vout = Ma \sin \omega t.$  (15)

When *Ma* is lessened than 0.33, three levels are generated. When Ma is within the interval of 0.33 and 0.66, the output voltage level has five levels, and with an *Ma* greater than 0.66, it displays seven output voltage stages.

Fig. 2. Switching pattern for generating the seven-level PWM output voltage.

| Ma   | Ma < 0.33 | 0.33 < Ma < 0.66          | Ma > 0.66                  |

|------|-----------|---------------------------|----------------------------|

| On 🔪 |           |                           |                            |

| θ1   | π/2       | Sin <sup>-1</sup> (Ac/Am) | Sin <sup>-1</sup> (Ac/Am)  |

| θ2   | π/2       | π/2                       | Sin <sup>-1</sup> (2Ac/Am) |

| θ3   | π/2       | π/2                       | π - θ2                     |

| θ4   | π/2       | π -θ1                     | $\pi - \theta 1$           |

| θ5   | 3π/2      | $\pi + \theta 1$          | π +θ1                      |

| θ6   | 3π/2      | 3π/2                      | π +θ2                      |

| θ7   | 3π/2      | 3π/2                      | 2π-θ2                      |

| θ8   | 3π/2      | 2π -θ1                    | $2\pi - \theta 1$          |

TABLE I

SWITCHING ANGLES ACCORDING TO THE MODULATION INDEX

## 3. FPGA IMPLEMENTATION

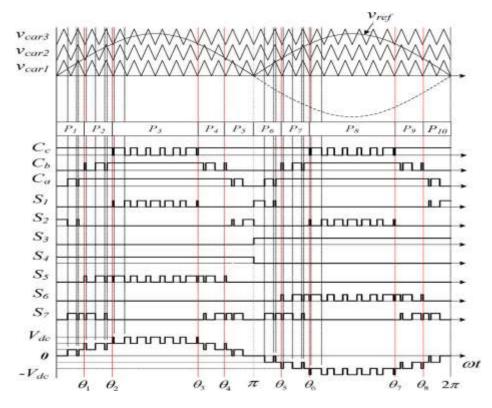

The Xilinx ISE design suite 14.3 software used to design the circuit. This software tool for HDL design made by Xilinx intended for synthesis and analysis, then implementing the designer to compile their designs, carry out timing analysis, explore the RTL diagrams, simulate a design's reaction to different stimuli, and design the target device with the programmer. The VHDL code for seven level PWM has been written into the Xilinx ISE design suite. The simulation was validated in the MODELSIM 6.4 a ISE simulator. For generating the sine wave using VHDL program ,the values are taken from the Matlab/simulink.

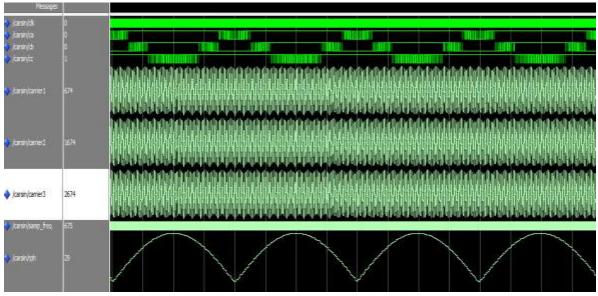

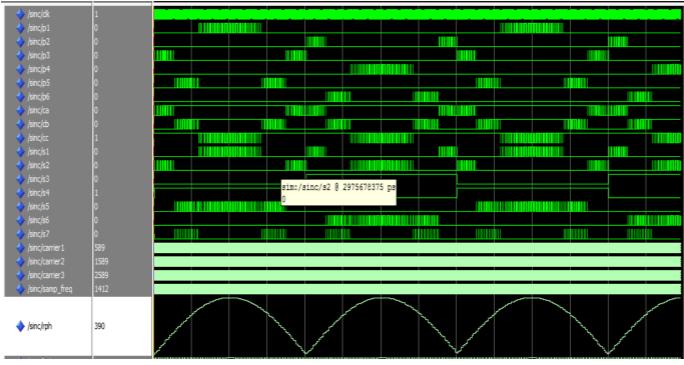

Fig 3.Generation of carrier and reference signal

Then comparing the three carriers and sine wave command signals  $C_a, C_b, C_c$  are generated.

Fig 4.Generation of command signal

By using the generated command signal switching signals are simulated. The  $period(P_n)$  is generated according to the switching angle. By using the logical combination of command signals and

period  $(P_n)$  seven switching signals are generated. Figure.5.shows the generation of switching signal using vhdl coding.

Fig.5.Generation of switching signals

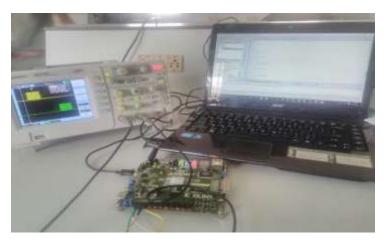

The figure 6.shows the FPGA implementation setup for switching signals using Xilinx SPARTAN6 FPGA kit. The simulated switching signal is displayed by DSO.

# Fig.6.FPGA implement setup using Xilinx SPARTAN6 FPGA kit.

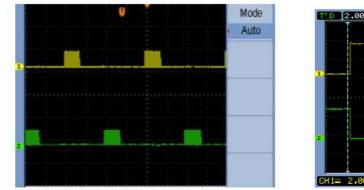

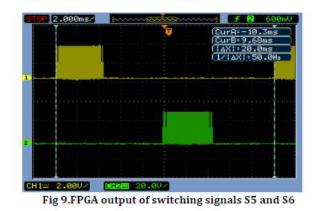

The output of generation of seven level switching signals using Xilinx Spartan 6 kit shown in the figure 7-

Fig 7. FPGA output of switching signals S1 and S2

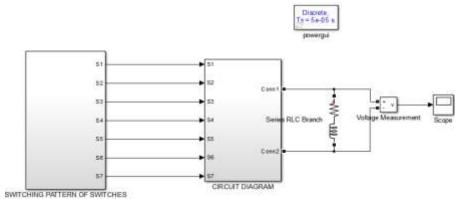

The seven level PWM inverter which is also validated using MATLAB/SIMULINK using phase disposition switching technique. Fig 11 shows the simulation diagram of seven level PWM inverter, which includes two subsystem block. One

Fig 8. FPGA output of switching signals S3 and S4

Fig 10.FPGA output of switching signal S7

subsystem block contains the switching pattern and other subsystem block includes the circuit diagram then RL load is connected across the output.

#### Fig 11. Simulation diagram of seven level PWM inverter

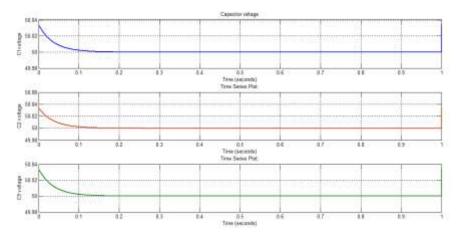

The input dc voltage is fixed to dc 150 V; hereafter, each series-linked capacitor voltage is equally energised into dc 50 V. The frequency of an output voltage is set to 60 Hz.

Fig 12. Output of three series-connected capacitors

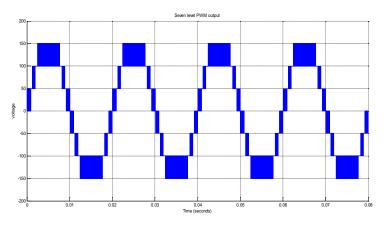

Fig 13.Output waveform of seven level PWM inverter

#### 4. CONCLUSION

In this manuscript we projected a PWM multilevel inverter that can meritoriously up surging the number of output voltage levels with a solitary dc voltage source. With the intention of produce the seven-level output voltage, the recommended multilevel inverter requires a single dc voltage source employing three series linked capacitors, two diodes, three active switches for producing the output voltage stages, and an H-bridge cell which is used to generate the polarity. The recommended 7-level PWM inverter can be a best choice, which can auxiliary for the orthodox PWM inverters.

#### Acknowledgement

First and foremost, we would thank god almighty for blessing us with enthusiasm, courage, knowledge and energy to help us finish our M.E final

year project. We thankful to our management for support and guidance and encouragement in making this project possible.

Our sincere thanks to all the lectures who helped us in many ways, gave valuable advises and make our journey easy.

#### REFERENCES

- 1. M. F. Kangarlu and E. Babaei, "A generalized cascaded multilevel Inverter using series connection of submultilevel inverters," IEEE

- Trans. Power Electron., vol. 28, no. 2, pp. 625–636, Feb. 2013.A. Mokhberdoran and A. Ajami, "Symmetric and asymmetric design and implementation of new cascaded multilevel inverter topology,"IEEE Trans. Power Electron., vol. 29, no. 12, pp. 6712–6724, Dec. 2014.

- 3. S. Gautam and R. Gupta, "Switching frequency derivation for the cascaded multilevel inverter operating in current control mode using multiband

hysteresis modulation," IEEE Trans. Power Electron., vol. 29, no. 3, pp. 1480–1489, Mar. 2014.

- M. M. Renge and H. M. Suryawanshi, "Five-level diode clamped inverter to eliminate common mode voltage and reduce dv/dt in medium voltage rating induction motor drives," IEEE Trans. Power Electron., vol. 23, no. 4, pp. 1598–1607, Jul. 2008.

- J. Huang and K. A. Corzine, "Extended operation of flying capacitor multilevel inverters," IEEE Trans. Power Electron., vol. 21, no. 1, pp.140–147, Jan. 2006.

- A. Ajami, M. R. J. Oskuee, A. Mokhberdoran, and A. Van den Bossche, "Developed cascaded multilevel inverter topology to minimize the number of circuit devices and voltage stresses of switches," IET Power Electron., vol. 7, no. 2, pp. 459–466, Feb. 2014

- K.-M. Tsang and W.-L. Chan, "Single DC source three-phase multilevel inverter using reduced number of switches," IET Power Electron., vol. 7, no. 4, pp. 775–783, Apr. 2014.

- 8. J. Dixon and L. Moran, "High-level multistep inverter optimization using a minimum number of power transistors," IEEE Trans. Power Electron., vol. 21, no. 2, pp. 330–337, Mar. 2006.

- 9. K. K. Gupta and S. Jain, "Comprehensive review of a recently proposed multilevel inverter," IET Power Electron., vol. 7, no. 3, pp. 467–479,Mar. 2014.

- J. Dixon et al., "Static Var compensator and active power filter with power injection capability, using 27-level inverters and photovoltaic cells," in Proc. IEEE Int. Symp. Ind. Electron., 2006, pp. 1106– 1111.

- M. Rotella, G. Penailillo, J. Pereda, and J. Dixon, "PWM method to eliminate power sources in a nonredundant 27-level inverter for machine drive applications," IEEE Trans. Ind. Electron., vol. 56, no. 1, pp. 194–201, Jan. 2009.

- Y. Ounejjar, K. Al-Haddad, and L. A. Greégoire, "Packed U cells multilevelconverter topology: Theoretical study and experimental validation,"IEEE Trans. Ind. Electron., vol. 58, no. 4, pp. 1294–1306, Apr. 2011.

- J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new multilevel converter topology with reduced number of power electronic components," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 655–667, Feb. 2012.

- E. Babaei, "A cascade multilevel converter topology with reduced number of switches," IEEE Trans. Power Electron., vol. 23, no. 6, pp. 2657–2664, Nov. 2008.

- K. Wang, Y. Li, Z. Zheng, and L. Xu, "Voltage balancing and fluctuation suppression methods of floating capacitors in a new modular multilevel converter," IEEE Trans. Ind. Electron., vol. 60, no. 5, pp. 1943–1954, May 2013.

- E. Najafi and A. H. M. Yatim, "Design and implementation of a new multilevel inverter topology," IEEE Trans. Ind. Electron., vol. 59, no. 11, pp. 4148–4154, Nov. 2012.

- Y. Hinago and H. Koizumi, "A single-phase multilevel inverter using switched series/parallel DC voltage sources," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2643–2650, Aug. 2010.

- N. A. Rahim, K. Chaniago, and J. Selvaraj, "Singlephase sevenlevel grid-connected inverter for photovoltaic system," IEEE Trans. Ind. Electron., vol. 58, no. 6, pp. 2435–2443, Jun. 2011.

- A. Edpuganti and A. K. Rathore, "Optimal lowswitching frequency pulsewidth modulation of medium voltage seven-level cascade-5/3H inverter,"IEEE Trans. Power Electron., vol. 30, no. 1, pp. 496–503, Jan. 2015.

- J. Mei, B. Xiao, K. Shen, L. M. Tolbert, and J. Y. Zheng, "Modular multilevel inverter with new modulation method and its application to photovoltaic grid-connected generator," IEEE Trans. Power Electron., vol. 28, no. 11, pp. 5063–5073, Nov. 2013.

- A. Ajami, H. Shokri, and A. Mokhberdoran, "Parallel switch-based chopper circuit for DC capacitor voltage balancing in diode-clamped multilevel inverter," IET Power Electron., vol. 7, no. 3, pp. 503-514, Mar. 2014